# Digital Technical Journal

of Digital Equipment Corporation

#### **Cover Design**

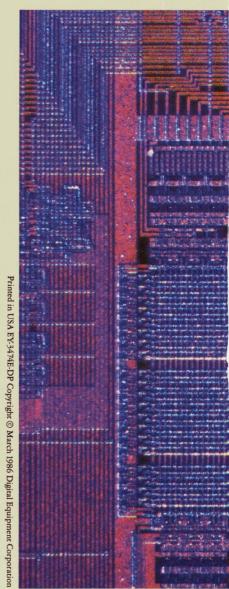

Hardware, software, and peripheral devices for the MicroVAX II system are featured in this issue. Two VLSI devices, the 78032 CPU chip and the 78132 FPU chip, form the core of this system. Our cover shows the input programmable logic array for the FPU chip.

The cover was designed by Deborah Falck of the Graphic Design Department.

#### Editorial Staff

Editor - Richard W. Beane

#### Production Staff

Production Editor – M. Terri Autieri Designer – Charlotte Bell Typesetting Programmer – James K. Scarsdale

#### **Advisory Board**

Samuel H. Fuller, Chairman Robert M. Glorioso John W. McCredie John F. Mucci Mahendra R. Patel Grant F. Saviers William D. Strecker Maurice V. Wilkes

The *Digital Technical Journal* is published by Digital Equipment Corporation, 77 Reed Road, Hudson, Massachusetts 01749.

Comments on the content of any paper are welcomed. Write to the editor at Mail Stop HL02-3/K11 at the published-by address.

Comments can also be sent on the ENET to RDVAX::BEANE or on the ARPANET to BEANE%RDVAX.DEC@DECWRL.

Copyright © 1986 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. Requests for other copies for a fee may be made to the Digital Press of Digital Equipment Corporation. All rights reserved.

The information in this journal is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

ISBN 932376-89-4

Documentation Number EY-3474E-DP

The following are trademarks of Digital Equipment Corporation: CompacTape, DEC, the Digital Iogo, MicroVAX, MicroVAX I, MicroVAX II, MicroVMS, PDP-7, PDP-11, Q-BUS, RSTS, TK50, ULTRIX, ULTRIX-32, UNIBUS, VAX, VAX-11/730, VAX-11/750, VAX-11/780, VAX 8600, VAX 8200, VAXELN, VAXstation, VMS, VT.

Apple II is a trademark of Apple Computer, Inc. AT&T is a trademark of American Telephone & Telegraph Company.

IBM is a registered trademark of International Business Machines, Inc.

Mylar is a trademark of E. I. duPont deNemours & Company.

Tek is a registered trademark of Tektronix, Inc. UNIX and System V are trademarks of AT&T Bell Laboratories.

Xerox is a registered trademark of Xerox Corporation. 68000 is a trademark of Motorola, Inc.

8086 and Intel are trademarks of Intel Corporation.

The manuscript for this book was created using generic coding and, via a translation program, was automatically typeset. Book production was done by Educational Services Media Communications Group in Bedford, MA.

# Contents

| 8 | Foreword        |   |

|---|-----------------|---|

|   | Jeffrey C. Kalb | ) |

12 The MicroVAX 78032 Chip, A 32-Bit Microprocessor

Daniel W. Dobberpuhl, Robert M. Supnik, Richard T. Witek

**New Products**

- 24 **The MicroVAX 78132 Floating Point Chip**William R. Bidermann, Amnon Fisher, Burton M. Leary,

Robert J. Simcoe, William R. Wheeler

- 37 Developing the MicroVAX II CPU Board

Barry A. Maskas

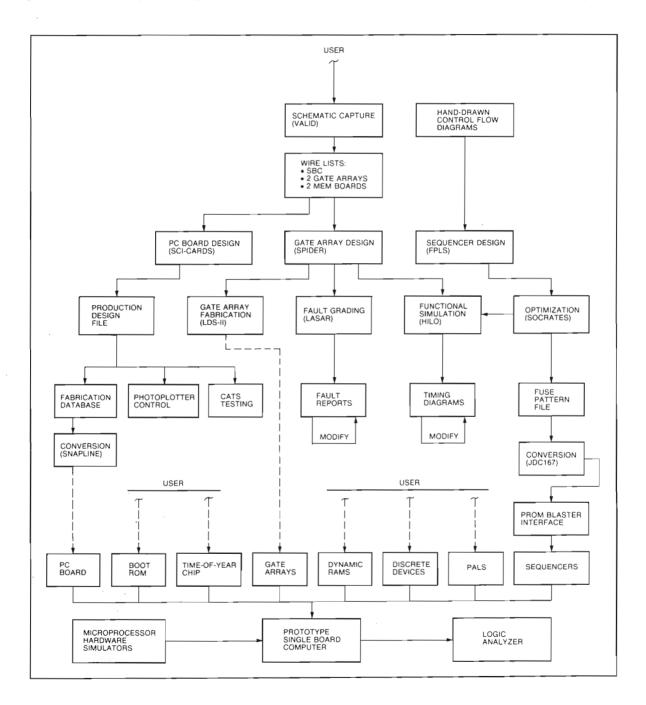

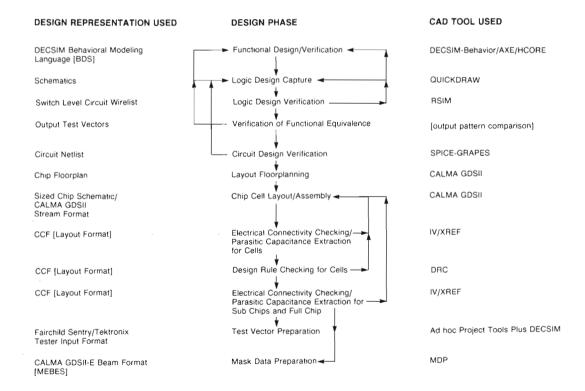

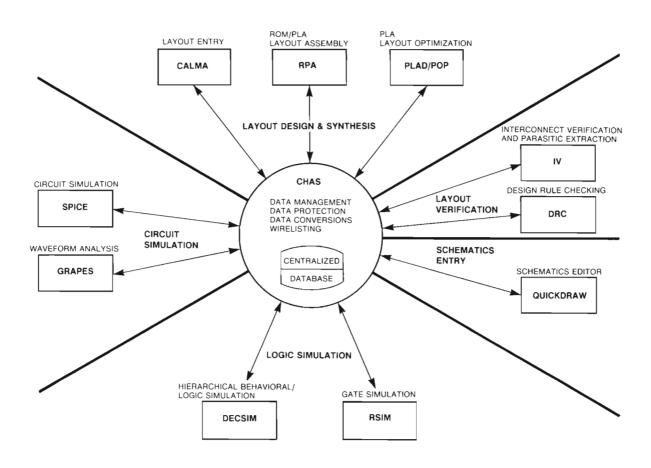

- 48 The Evolution of the Custom CAD Suite Used on the MicroVAX II System

Anthony F. Hutchings

- 56 The Making of a MicroVAX Workstation Rick Spitz, Peter George, Stephen Zalewski

- 66 The RQDX3 Design Project

Nicholas A. Warchol, Stephen F. Shirron

- 76 The Evolution of Instruction Emulation for the MicroVAX Systems Kathleen D. Morse, Lawrence J. Kenah

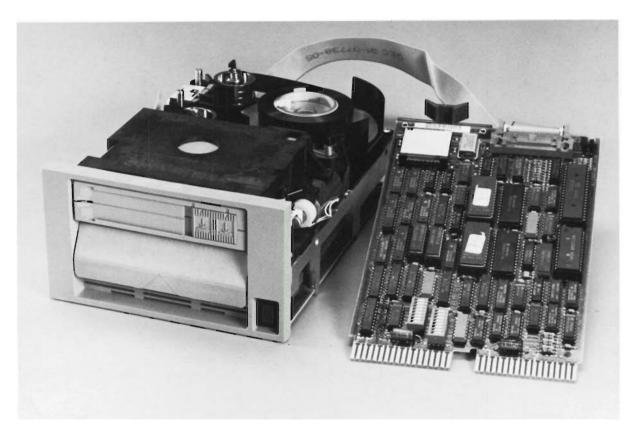

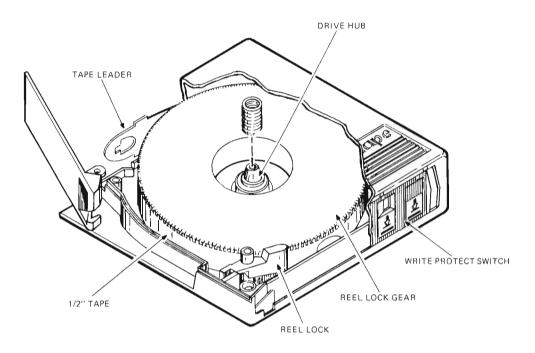

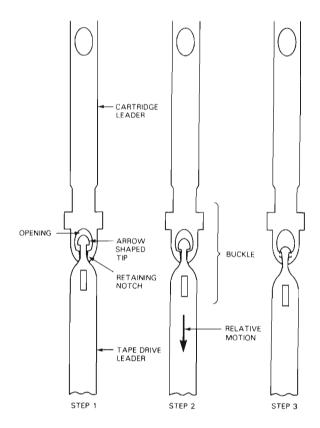

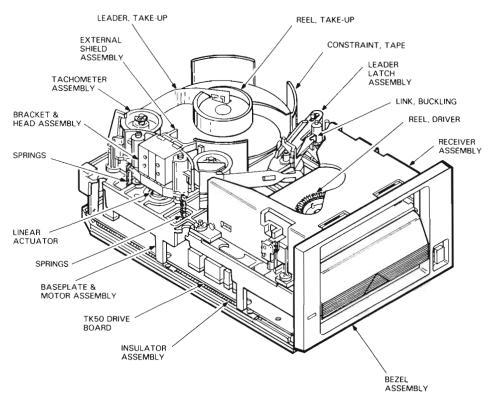

- 86 **The TK50 Cartridge Tape Drive** Steven E. Boone, Guenter E. Schneider

- 99 Porting ULTRIX Software to the MicroVAX System

Raymond J. Lanza

# Editor's Introduction

Richard W. Beane

This issue of the journal is the second published by Digital's engineering organization. Our first issue (August 1985) featured papers about the technologies used in designing the VAX 8600 processor. The journal presents papers written by the technical contributors who design Digital's products. The information is directed at engineering faculty members, Digital's own engineers, and customers.

This issue features the MicroVAX II system, which implements the VAX architecture on a single CPU chip, the 78032. Another chip, the 78132, executes fast floating point operations; a single board holds both those chips, plus one megabyte of memory. New peripherals have been designed, and the VMS and ULTRIX software adapted to the MicroVAX II system. This collection of papers, by authors from different engineering groups, presents a wide spectrum of the MicroVAX II hardware and software.

The first paper, by Dan Dobberpuhl, Bob Supnik, and Rich Witek, is a description of the 78032 CPU chip, which implements a subset of the full VAX instruction set. The decisions about which instructions to microcode are discussed, along with hardware simplifications needed to fit functions on one chip. The chip's various operations are explained, with emphasis on parallel execution.

The CPU chip can use a coprocessor, the 78132 FPU chip, to perform fast floating point operations. The paper by Bill Bidermann, Amnon Fisher, Mike Leary, Bob Simcoe, and Bill Wheeler relates the 78132's architecture and algorithms. The protocol between the two chips is discussed and a

description is given of the wiring and signal integrity issues and how they were addressed.

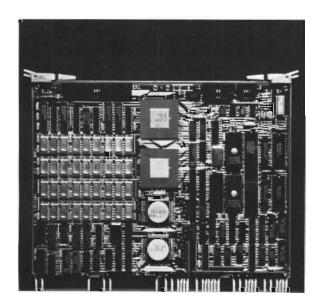

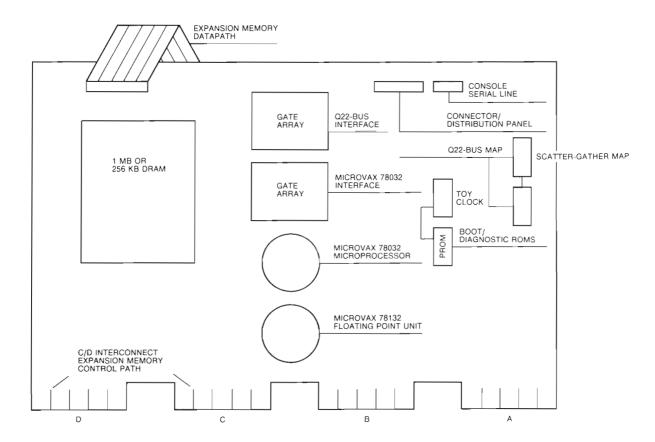

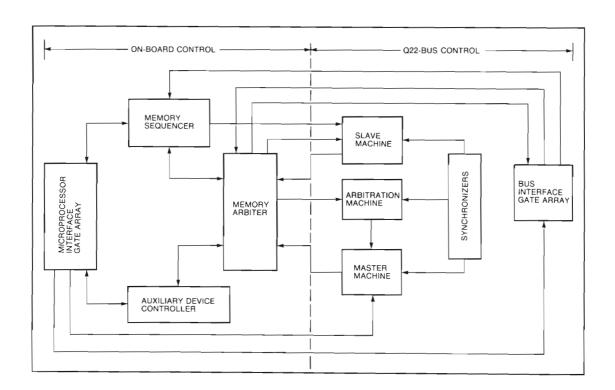

Both chips are mounted on a single board containing one megabyte of memory. Barry Maskas' paper explains how the CPU board had to be designed as a linked sequential machine with dual ports. The development process is interesting because the board and the chips were designed in parallel.

The paper on CAD tools, by Tony Hutchings, relates the large role they played in the chip and board designs. The various levels of CAD support, from behavioral modeling, through logic and circuit simulation, to wirelist generation is described.

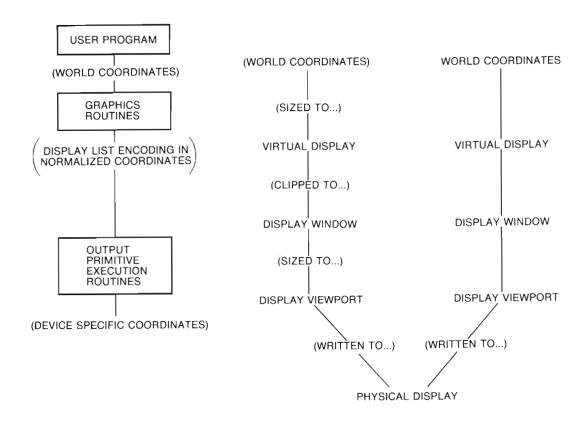

The software graphics that turn the MicroVAX II system into a single-user workstation are reported in the paper by Rick Spitz, Peter George, and Steve Zalewski. The control of windowing software and virtual displays is discussed, as are the implementation details.

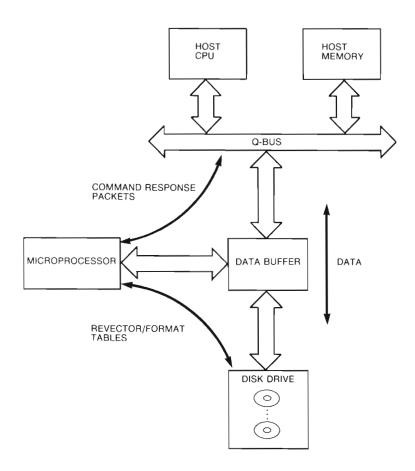

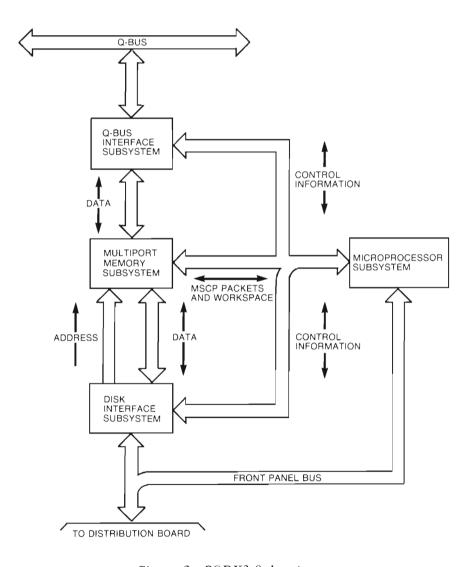

The RQDX3 disk controller provides fast data transfers between a CPU and disk storage devices. Nick Warchol and Stephen Shirron explain the top-down development process that lead to unique solutions to difficult problems. Their description of the final architecture shows how the original goals were met in the eventual design.

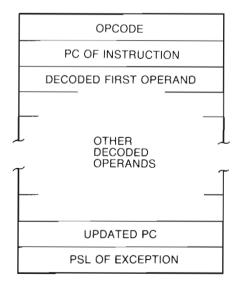

With a subset architecture, those instructions not in the set have to be executed another way. The paper by Kathy Morse and Larry Kenah describes the macrocode emulation of the VMS changes required to do that. The testing techniques are interesting since they were done without MicroVAX hardware.

The paper by Steve Boone and Guenter Schneider describes the TK50, a streaming cartridge tape drive providing fast data transfer. The authors discuss the unique cartridge, tape transport, and controller designs, highlighting the self-threading technique and the serpentine read/write process.

The final paper, by Ray Lanza, describes porting the ULTRIX-32 software to the MicroVAX processor. Ray explains the cross-development environment and the mapping techniques that allowed the heart of the ULTRIX software to fit on a small system.

Dick Beane

# **Biographies**

William R. Bidermann Bill Bidermann is the engineering manager of the Advanced Development Memory Group. He consulted on the floating point chips for both the VAX 8200 and MicroVAX II processors. Before joining Digital in 1984, he was a consultant for Tenex and Rampower. Previously, he worked as a project manager at Hewlett Packard Laboratories in Palo Alto, California, and as a design engineer at Texas Instruments Central Research Labs. Bill received his S.B. and S.M. degrees in electrical engineering and computer science from M.I.T. in 1978.

Steven E. Boone Steve Boone graduated from Michigan State University (B.S.E.E., 1974) and the University of Michigan (M.S.E.C.E., 1975). He has also done advanced graduate work at Southern Methodist University. Before joining Digital in 1984, Steve worked as a principal hardware engineer for Sequoia Systems, and as a senior design engineer at Prime and Raytheon. For two years, he was an engineering supervisor working on the TK50 controller design. Steve is currently the technical engineering manager for TK Cartridge Tape Subsystem Engineering.

Daniel W. Dobberpuhl Dan Dobberpuhl is a senior consulting engineer and manager of the Processor Advanced Development Group. On the MicroVAX II project, he led the implementation of the 78032 CPU chip. Previously, he consulted on CMOS, ZMOS, and TIPI technology development, and worked on the T11 and F11 projects. Dan joined Digital in 1976 from General Electric Company. He received a B.S.E.E. degree from the University of Illinois in 1967. A member of IEEE, he holds four patents and is the coauthor of *The Design and Analysis of VLSI Circuits*.

Amnon Fisher Educated at Israel Institute of Technology (B.S.E.E., 1973) and City College of New York (M.S.E.E., 1975), Amnon Fisher worked as both a contributor and project leader on the 32016 CPU at National Semiconductor. Joining Digital in 1983, he was a project leader of the V11/SCORPIO floating point chip (VAX 8200 system), and a contributor to the MicroVAX II 78132 chip. Amnon is currently an engineering manager in the Semiconductor Engineering Group, working on the design and development of a four-chip set VAX implementation.

**Peter C. George** Earning his bachelors and masters degrees in computer science and engineering from M.I.T. in 1980, Peter George joined the VMS Development Group in that year. He first worked on VMS user interfaces, then on the workstation software as a principal engineer on the VAXstation project. Peter is currently a project leader, working on advanced workstation software projects. Peter is a member of ACM, and the national honor societies Tau Beta Pi, and Eta Kappa Nu.

Anthony F. Hutchings Tony Hutchings received his B.S. degree from the University of Newcastle On Tyne in 1965. At ICL in the U.K. for 16 years, he designed operating systems and was one of the VME-system architects on the 2900 series. He later became corporate manager of CAD. Tony joined Digital in 1982 as the project manager for the proprietary DECSIM software and then became manager of the VLSI CAD Group. Tony, a member of IEEE and the British Computer Society, is currently chairman of the CAD section of the ICCD.

Lawrence J. Kenah Larry Kenah, a consulting software engineer in the VMS Development Group, wrote the decimal/string emulator for the MicroVAX project. Since joining engineering in 1980, Larry has worked on the VMS nucleus in the areas of memory management, process scheduling, and image activation. He came to Digital in 1975 as an instructor and course developer in Educational Services. Larry received his B.S. degree (1968) from Boston College and his M.S. (1970) and Ph.D. (1977) degrees in high-energy physics from Northwestern University. He is coauthor of *VAX/VMS Internals and Data Structures*.

Raymond J. Lanza Ray Lanza is currently the project leader for the ULTRIX-32 system. After joining Digital in 1983, he ported the ULTRIX system to the MicroVAX I processor. As project leader, he ported the system to the MicroVAX II processor in 1984. Ray received his B.S.E.E./C.E. degree from the University of New Hampshire in 1980, then became the lead engineer in a UNIX group at AT&T. Later he was a senior software engineer at Wang Laboratories, Inc., researching windowing systems and UNIX distributed systems.

Burton M. Leary In 1980, Mike Leary joined Digital after receiving his B.S. degree in electrical engineering from the University of Massachusetts. In semiconductor engineering, he worked on chip designs and helped to develop the floating point chip for the MicroVAX II system. Mike did behavioral modeling, wrote microcode, and designed the main sequencer for that chip. He is now a senior engineer in the Advanced Development Memory Group, designing the internal cache for an advanced chip project.

Barry A. Maskas Barry Maskas is a principal engineer currently specifying and designing an integrated circuit, and fiber-optic boards for future systems. As a senior engineer on the MicroVAX II project, he was co-designer of the CPU board and the memory boards. Barry came to Digital in 1979 after receiving his B.S.E.E. degree from Pennsylvania State University. He also holds an associate's degree from the Community College of Allegheny County and did undergraduate work at LSU. Barry is a member of Eta Kappa Nu; he has a patent pending for a self-configurable memory subsystem.

Kathleen D. Morse As a consulting software engineer, Kathy Morse is responsible for VMS support on all low-end CPUs and peripherals. Earlier, she did the VMS support for both MicroVAX systems, the VAX 11/782 system, and the MA780 multiport memory. Kathy joined Digital in 1976 after receiving her B.S.C.S. degree from Worcester Polytechnic Institute, where she also earned her M.S.C.S. degree in 1985. Kathy is a member of IEEE, the Professional Council, and ACM, as well as Tau Beta Pi and Upsilon Phi Epsilon. She has published in the Computer Measurement Group's 1985 Conference Proceedings, and *Datamation*.

Guenter E. Schneider Guenter Schneider joined the Mass Storage Group in 1970, when it had only about 25 people. He has worked on the designs for the RX05, RL01, RX02, TU58, RX50, and RD50/51 storage devices. As a consulting engineer, he helped to design the TK50 cartridge tape drive. Guenter received a Diplom Ingenieur from the Technische Hochschule Aachen in West Germany and his M.S.M.E. degree from M.I.T. in 1969. He holds two patents, with a third pending, and is a member of the engineering society Verein Deutscher Ingenieure.

**Stephen F. Shirron** Educated at Catholic University of America (B.S., 1980 and M.S., 1981), Stephen Shirron came to Digital after graduating Summa Cum Laude. As a senior software engineer, he developed an interpreter for VAX/Smalltalk-80 and designed the VAXstation 100 firmware. Currently a principal software engineer, Stephen designed and implemented the firmware for the RQDX3 disk controller. He is a member of Phi Beta Kappa and has written a chapter in *Smalltalk-80: Bits of History, Words of Advice*.

Robert J. Simcoe Bob Simcoe is a technical manager currently working on serial interconnect products. He was the technical manager for the floating point chips in both the MicroVAX II and VAX 8200 systems. Before joining Digital in 1982, Bob worked for the Department of Defense and General Electric Company. His duties involved MOS design, process development, and product design using custom ICs. Bob holds seven patents on IC circuitry and systems. He graduated from the University of Illinois (B.S.E.E., 1966).

**Rick Spitz** Rick Spitz manages VAX/VMS software development for CPUs and peripherals. As a consulting software engineer, he was a primary member of the architectural design team on the MicroVAX workstation project. Rick designed the VMS graphics hardware interface architecture and, for six years, has specialized in VAX/VMS hardware-software interfaces. He joined Digital in 1977 as a senior software specialist and received Digital's Software Excellence Award. Previously, Rick developed microprocessor software for Inco, Inc. He earned a B.S.E.E. degree from Clemson University in 1974 and his M.S.C.E. degree from the University of Lowell in 1983.

Robert M. Supnik Bob Supnik is a corporate consultant and group manager in semiconductor engineering. On the MicroVAX CPU chip project, he was project leader and lead microprogrammer. Bob was the project manager for the J11, a contributor to the F11, and supervised advanced development on the HSC50 and UDA50. Before joining Digital in 1977, he worked at Applied Data Research. Bob received his S.B. degrees (1967) in math and history from M.I.T. and his M.A. degree (1972) in history from Brandeis University. He received *Science Digest's* "100 Top Innovators of 1985" award.

Nicholas A. Warchol In 1977, Nick Warchol joined Digital after receiving his B.S.E.E. degree (cum laude) from the New Jersey Institute of Technology. Later he earned his M.S.E.E. degree from Worcester Polytechnic Institute in 1984. He is a member of Tau Beta Pi and Eta Kappa Nu. Nick has worked on the advanced development of charged-couple device memories, bubble memories, and laser video disks. In his present position as a principal engineer, he worked on the design of the RQDX3 disk controller.

William R. Wheeler After earning his B.S.E.E. degree in 1982 and his M.S.E.E. degree in 1983 from Cornell University, Bill Wheeler came to Digital as a junior engineer. On the MicroVAX II project, he designed the exponent datapath and control for the 78132 floating point chip. Later he designed the exponent section of the floating point chip in the VAX 8200 system. Bill is currently working on the instruction box and bus interface unit for a new microprocessor chip.

Richard T. Witek Rich Witek is a consulting engineer working on the architecture and implementation of new microprocessors. He helped to develop and debug the MicroVAX 78032 CPU chip. Rich also worked on implementing DECnet/E and on the DECnet Architecture Review Group during Phases 2 and 3. He also worked in the VLSI CAD group. Before joining Digital in 1977, Rich was a senior technical associate at AT&T Bell Laboratories and an engineering assistant at Argonne National Laboratory. He received his B.A. degree in computer science from Aurora College, and is a member of ACM and IEEE.

**Stephen H. Zalewski** Steve Zalewski is a senior software engineer working on the graphics execution routines for the VAXstation II/GPX system. He joined Digital in 1981 after receiving his B.S. degree in computer engineering from Worcester Polytechnic Institute. Steve developed the graphics device driver for the VAXstation I and II systems. His earlier work involved writing RMS file-sharing internals and implementing RMS file sharing and global buffers for VAXcluster software.

Jeffrey C. Kalb Vice President and Group Manager Large Scale Integration

The roots of the MicroVAX program go back to the summer of 1981. To understand why this program was initiated and the thinking behind it, one has to look at the events of that time. Many developments were taking place, suggesting that a whole new class of systems capabilities could emerge before long.

The VAX-11/780 system was in its heyday. It was recognized as the standard against which all other computers were compared and benchmarked. And true to fashion, everyone seemed to find some way to benchmark his machine in some particular niche against the 11/780's capabilities. That was particularly true of the upcoming generation of microprocessors and microprocessor-based systems. The universities were busily benchmarking Intel Corporation's latest generations of 8086s, 80186s, and the early 80286s on specific jobs. The same was true of the 68000based system. Many companies were starting to come to market with engineering workstations and similar products based on these microprocessor chips. In fact if one believed the trade press, the VAX-11/780 system had actually been eclipsed in performance and capabilities by these "upstarts."

Needless to say, these events caused some degree of consternation and soul-searching within Digital Equipment Corporation. Moreover, another factor was becoming painfully obvious: the emergence of the independent software vendors. Hoards of small companies were springing up everywhere to generate software for various personal computers that either had already been introduced to the marketplace, like the Apple II, or shortly would be, like the IBM PC. These small vendors wanted to write software for the systems that had the highest market volume. Their reasoning was clear. To sell as many of their software packages as possible required implementing their ideas on the highest volume hardware. It was also clear that the highest volume hardware was going to be microprocessor based and quite inexpensive.

Meanwhile, within Digital, the Semiconductor Engineering Group (SEG) was busy developing a multichip implementation of the VAX architecture. Built with a midrange, multiuser, high-performance system in mind, this chip set and its attendant system implementations were aimed at the marketplace for systems above \$50 thousand. CAD tools were being developed and manufacturing processes developed and refined. The module and system concepts were then in the definition stage.

Discussions began at this time, centered around what was later known as the MicroVAX system. There was a perceived need to counter the rising tide of encroachment on our systems business by microprocessors. We wanted to create systems with volumes high enough to warrant the attention of the independent software vendors. In general, we wanted to establish the VAX architecture as one of the preferred architectures at all potential price levels in the entire industry.

These discussions and strategic thinking converged after receiving an unsolicited proposal from a semiconductor manufacturer. This firm had approached us during that summer, wanting to implement the VAX architecture in one or two high-performance chips. This set of chips could be used in our systems and sold as standalone products. The firm wanted to use the VAX/VMS architecture (and primarily the software associated with it) to get a jump in the marketplace by establishing a high-volume architectural standard at the 32-bit level. We were concerned from the beginning that the capabilities and resources of this smaller firm would not be sufficient to execute such a formidable program. But the notion that building a single-chip VAX implementation and using it to counter-attack the emerging microprocessorbased systems had struck a responsive chord. Until that time, our thinking had been in terms of our traditional price/performance learning curves. Our strategies did not include extraordinarily low-priced VAX systems.

As indicated above, the Semiconductor Engineering Group in Hudson, Massachusetts, was already heavily committed to the multichip

VAX system. A number of other major chip projects were in development as well. Therefore, we searched for a larger semiconductor vendor who could bring additional design and manufacturing resources to bear on this concept. Such a vendor could also make available additional distribution channels for sales of high-volume chips to the general marketplace. This line of thinking was pursued with various vendors throughout the fall and winter of 1981, until April 1982.

Interestingly enough, there was less than wholehearted enthusiasm on the part of the various vendors who were approached. Each of them had already decided on an approach to the problem and were unwilling to make the development of the MicroVAX chip a priority item. That commitment was an extremely important issue to us. Experience had shown that complex projects of this nature always exceeded the schedules and the budgets anticipated when they received second-class attention within the merchant semiconductor industry. Thus one criteria for working with a vendor was that he commit to the MicroVAX architecture as a primary market thrust. No one was willing to do that.

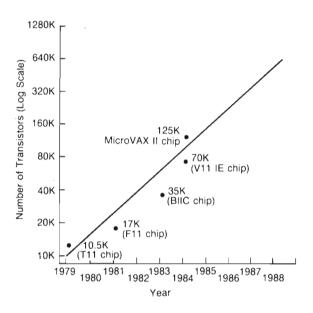

At the same time, other issues had to be worked. It was clear that the full VAX architecture as implemented in the multichip set could not easily be put on a single chip. That would have taken over 1 million transistors, a capability that would not be available until the end of the decade. Therefore, early in the project, we recognized that there was a need to subset the architecture to make it implementable on a single chip. By December 1981, the idea of developing a single-chip VAX implementation was beginning to get some positive re-enforcement within Digital. As a result, in that month, Gordon Bell, then vice-president of Engineering, chartered a subcommittee to investigate what should be included in a MicroVAX architecture.

The key people involved were Roy Moffa, who had been leading the strategic thinking about a single-chip VAX system; Bob Supnik, representing semiconductor technology; Dick

Hustvedt and Dave Cutler, representing software technology; and Bill Strecker, representing VAX architecture technology. After a few intensive meetings, they proposed a subset of the VAX architecture in January 1982. Bob Supnik and the semiconductor technologists thought that this subset could be implemented in a single chip. This new architecture would be modified slightly later in the year, but it is essentially the architecture that exists today. The only significant modification was in the memory management capability, and in some sense, this change actually simplified the development of the chip.

In parallel with these other activities, Bob Supnik and other members of SEG had been studying ways to get the chip developed internally. They were hoping to leverage the existing investments in process technology, chip modeling, CAD tools, and the various other elements that were necessary. Furthermore, and highly significant to the whole program, they developed ways of re-using some of the investments being made in the multichip VAX implementation and other programs already in progress. As a result the floating point chip being developed for a PDP-11 microprocessor was used as the building block for the MicroVAX implementation. Not only that but the chip was also retrofitted back into the existing multichip set to minimize the workload. Moreover, the datapath was lifted from the instruction/execution unit of the multichip set to form the backbone of the MicroVAX CPU. Tools and techniques were borrowed whenever it was possible.

In this sense the MicroVAX program was unique. There were almost nine months of strategy discussion and evaluations of various ways of implementing and executing before any real design actually started. While many of the proposed business strategies were never adopted, they at least received a hearing. In any case the die was cast.

The real implementation of the MicroVAX chip did not get started until June 1982, the official start date being July 6, 1982. (Some work had been done prior to that for recruiting

and staffing.) It was soon evident that there were some key elements that had to be addressed. The first was CAD tools. There was no question that this device had to be simulated extensively at all levels of implementation. There was no other way to get the quality of design and performance levels being planned. At the time the program started, these tools were mostly experimental. Some techniques had been tested, but the reality was that CAD tools "broke" on numerous occasions during the development of the system. Crisis-oriented SWAT teams had to be put in place to bridge over or break through barriers that threatened to bring the entire program to a halt.

There was another equally important element. The entire program was an extremely complicated one, with many elements on parallel paths. Process technology had to be developed, CAD tools developed and refined, chip designs done, systems implementations executed, and test techniques and equipment developed. Each of those elements was intimately entwined with the others. Therefore the possibility clearly existed that, upon reaching the end of the design, we would be faced with debugging a new process technology, a new manufacturing line, new testers, a new chip design, new packages, and a new system, all simultaneously. A real possibility existed that we couldn't separate the variables in a sufficiently clear and timely manner to allow the chip debugging and system evaluation to take place. This phase could last for months or perhaps even years, something that has happened before on many such programs in the merchant industry.

To avoid that, we segmented the major risks in the program and put plans in place to minimize as many of those as possible in parallel before the new chip arrived. For instance, rather than debugging an entirely new manufacturing line while trying to build this new chip, we combined the existing two wafer fabrication lines into one. The smaller line was then retrofitted to provide a pilot line capability. That gave us a trained staff, a debugged facility, and all the other elements necessary to mini-

mize the interaction of the process and facility. Additionally, a test vehicle was designed so that manufacturing could run wafers, debug process steps, and improve the basic yields of the process well before the new chip arrived. In the test area, test programs were implemented on older, proven testers on which the engineers had experience. That worked even though we knew that, for the eventual production, an entirely new generation of testers would be necessary to precisely test such a complicated device at its full speed.

Similarly, other areas, such as packaging, CAD tool development, and parts of the system evaluation, were examined and improved in parallel long before they had to work together. A major program was put in place to uncouple risks and to hire and train the workforce well in advance of the completion of the MicroVAX chip design. This effort was quite expensive; some people thought that much of the money was being thrown out with the materials that were made experimentally. But the end result was one of the smoothest debugs and introductions into chip manufacturing that I have ever witnessed for a complex device. While there were problems and although things didn't always work right, there were almost always independent ways of separating the variables in the problem. In that way it could be properly analyzed and corrections put in place. This example should serve us well with complex development programs in the future.

One other thing done to enhance the debug and ensure the quality at the system level was to co-locate the CPU module designers with the chip designers. In that way their interaction was enhanced and the rate of problem resolution greatly accelerated. The module team itself was exceptionally small for such a major program, consisting of only three primary engineering people. But this unique program environment featured a high degree of simulation, close proximity of the engineers (the MicroVAX chip team had only 20 people), and heavy reliance on thorough evaluation at every step.

The end result was very, very few bugs in either the chip or the system. In fact there were

fewer than 20 bugs that had to be corrected before the integrated chip and system were able to boot the operating system. It should be noted that this quality has continued to manifest itself in the rapid manufacturing ramp-up and the quality of the systems that have been generated. There were more engineering changes to the parts and the system to enhance our margin and ease of manufacture than there were to make the system functional in the first place. That is evidence of a fundamentally different approach to building systems.

As noted above, the MicroVAX program is quite unique, from its initial conception to the continuing efforts to enhance quality and productivity. From the initial conception of the strategy, through the organization of the people and problems, to the ongoing engineering activity around quality and ease of manufacture, this program has provided a new paradigm for program execution and management. Our hope is that, with this knowledge, people can emulate the success of this program while eliminating the errors. In so doing, Digital can greatly enhance its ability to build and manufacture high-quality systems in increasingly shorter periods of time.

# The MicroVAX 78032 Chip, A 32-Bit Microprocessor

The MicroVAX 78032 implements the VAX architecture on one chip. To do that, the instruction set was repartitioned to reduce the number of transistors. The instructions used most frequently are in microcode; others, notably floating point, are emulated in macrocode. Hardware was simplified by having a small address translation cache and no memory cache; however, full VAX memory management is supported. A fast 200-nanosecond microcycle allows instructions to execute in parallel. The CPU chip is made using a 3-micron, double-metal NMOS process. The control store ROM has X-shaped cells, which help to reduce its size.

The MicroVAX 78032 chip is the latest extension of the VAX architecture and the first in the form of a single-chip microprocessor. As the CPU of the MicroVAX II computer system, the 78032 performs nearly as fast as the VAX-11/780 superminicomputer, but in a microcomputer package.

# Origins and Goals

Digital began the MicroVAX CPU chip project in late 1981 in anticipation of increasing competitive pressures from industry-standard microprocessors. The original intent of the program was to license a semiconductor vendor to design and manufacture a MicroVAX single-chip microprocessor. However, the leading semiconductor companies were unable to meet the high-performance requirements and tight schedules that the project required. In May 1982, an internal development project was chartered to design the MicroVAX CPU chip.

From a designer's viewpoint, the development of this CPU was a challenging exercise in shrinking the VAX computer architecture without changing its function. There were five major goals that governed the design.

1. The kernel architecture was to be implemented on a single chip. Other chips or hardware could be used to improve performance or to provide additional func-

- tionality, but the basic VAX functions had to be incorporated in the base CPU design.

- 2. The chip had to be compatible with all VAX application programs. It had to execute any application program, whatever its size or complexity, written for any computer in the VAX family. And it had to execute without alterations to the program code. That meant that the chip had to run the MicroVMS and ULTRIX-32m (Digital's enhanced UNIX software) operating systems, and the VAXELN real-time kernel.

- 3. The chip had to perform at or near the speed of the VAX-11/780 processor. This goal implied that the chip had to have a highly parallel internal implementation, a high-performance external interface, and a fast microcycle. Accordingly, the internal microcycle of the chip was set at the same 200 nanoseconds (ns) as the 11/780's microcycle.

- 4. The price of the chip had to be competitive with commercial 32-bit microprocessors of comparable complexity. This required a relatively conservative die size and an inexpensive package. It also required the implemen-

tation of an external interface that was compatible with standard VLSI peripheral chips and demanded minimal support from the hardware on the CPU board.

5. The chip had to be designed and built quickly. To meet or beat competitive products, the chip had to be in production less than 2 ½ years after the start of development.

With these goals guiding the chip design team, the major problem was quickly identified: to reduce the number of transistors. That, in turn, required repartitioning the VAX instruction set and simplifying hardware functions wherever possible.

# Reducing the Number of Transistors

The principal problem in designing the 78032 was how to implement the complexity of the VAX architecture on a single chip. There are 304 instructions in the full instruction set, with 14 data types and 21 addressing modes. Instructions vary in length from 1 byte to 54 bytes. Demand-paged virtual memory support is required to guarantee compatibility with the operating system software. To accommodate this complexity in a full-scale VLSI VAX implementation requires about 1.25 million transistor sites. However, the semiconductor technologies available at the time of design could support only about one-tenth that number in a single-chip microprocessor. Seminary of the variable and the single-chip microprocessor.

The architectural functions in all VAX systems are partitioned among hardware, microcode, and the operating system. All previous VAX implementations have similar boundaries between these three. The hardware provides the registers and memory, the microcode provides the instruction set, and the operating system provides the program services. A large control store—a minimum of 400 kilobits (Kb)—is required to contain the instruction microcode. The console function is handled in either microcode or a support processor. Moreover, the control logic needed to support memory management and the variable instruction format is quite complex.<sup>4</sup>

Two different approaches were taken to reduce the transistor count in the microprocessor chip. First, the VAX instruction set was repartitioned to cut the size of the control store

to 62Kb. Second, the amount of on-chip hardware was reduced by simplifying some functions, placing others elsewhere, or omitting some altogether.

# Repartitioning the Instruction Set

As the first repartitioning step, the design team assumed that all VAX instructions had to be implemented in order to execute all VAX application software. However, there are several classes of instructions that involve a good deal of microcode and yet are infrequently executed. For example, a typical timesharing workload is handled by base instructions, scientifically oriented instructions, and commercially oriented instructions. Analyses of more than 70 million executed instructions showed that the commercially oriented ones represented less than 0.2 percent of the total executed.<sup>5,6</sup> Studies of scientific and engineering workloads showed even lower percentages. Even in commercial applications, the commercially oriented instructions represented less than 4 percent of the total executed, the majority being base instructions. Therefore, emulating the commercially oriented instructions in the operating system rather than using microcode would significantly reduce the size of the control store, but would have little effect on overall performance because these instructions were seldom executed.

On the other hand, floating point instructions require a good deal of microcode and are executed more frequently. Even with microcode, instruction execution is relatively slow unless a separate floating point accelerator (FPA) is used. Therefore, although existing VAX implementations offered both microcoded (warm) and hardware (hot) floating point, the design team decided not to implement these instructions in microcode. Instead, floating point instructions would be executed in an optional floating point chip, or by emulation using macrocode.

In total, 175 of the 304 VAX instructions and 6 of the 14 data types are implemented in onchip microcode. Those include integer and logical instructions, variable-bit field, control, queue, procedure calls, character string moves, and operating system support. This microcoded subset comprises over 98 percent of the instructions that are used to execute a typical program. However, the required microcode occupies only one-fifth the control store space of a full VAX implementation. Seventy floating point instructions and three data types (F, D, and G floating) are implemented in the floating point chip, when it is present. If that chip is absent, the instructions are emulated in macrocode. The remaining 59 instructions and 5 data types are always emulated in macrocode. Those are mainly decimal string, character string, and H floating point operations. The CPU chip provides some microcode support for the emulated instructions. Table 1 summarizes the instruction set architecture of the 78032 chip.

The decision to emulate instructions in macrocode has an effect on speed because emulated instructions take three to ten times longer to execute than microcoded instructions. However, the instructions in this group of 59 are

normally used so infrequently that the execution speed of a typical program is reduced by no more than four percent. Table 2 illustrates the division of instructions between the CPU chip, the FPU chip, and the macrocode. All in all, the fivefold reduction in the size of the control store halved what would have been the active area of the chip.

# Simplifying the Hardware Functions

The principal hardware simplifications in the 78032 are the reduced size of the address translation cache (translation buffer), and the elimination of a memory cache in favor of tightly coupled local memory.

As mentioned earlier, demand-paged virtual memory management was required for compatibility with the VAX architecture. Consequently, the design team decided that the 78032 would

Table 1 Instruction Set Architecture

| Implemented in CPU Chip      |     | in Implemented in Floating Point Chip |    | Implemented in Macrocode           |     |  |

|------------------------------|-----|---------------------------------------|----|------------------------------------|-----|--|

| Instructions:                |     |                                       |    |                                    |     |  |

| Integer and<br>Logical       | 89  | F floating                            | 24 | H floating                         | 28  |  |

| Address                      | 8   | D floating                            | 23 | Octaword                           | 4   |  |

| Variable Bit<br>Field        | 7   | G floating                            | 23 | Character<br>String                | 9   |  |

| Control                      | 39  |                                       |    | Decimal String                     | 16  |  |

| Procedure Call               | 3   |                                       |    | Edit                               | 1   |  |

| Miscellaneous                | 10  |                                       |    | CRC                                | 1   |  |

| Queue                        | 6   |                                       |    |                                    |     |  |

| Operating System<br>Support  | 11  |                                       |    |                                    |     |  |

| Character Move               | 2   |                                       |    |                                    |     |  |

| Total                        | 175 |                                       | 70 |                                    | 59  |  |

| Data Types:                  |     |                                       |    |                                    |     |  |

| Byte Integer                 |     | F floating                            |    | H floating                         |     |  |

| Word Integer                 |     | D floating                            |    | Octaword                           |     |  |

| Longword Integer             |     | G floating                            |    | Leading Separate<br>Numeric String |     |  |

| Quadword Integer             |     |                                       |    | Trailing Numeric Str               | ing |  |

| Variable Bit Field           |     |                                       |    | Packed Decimal                     |     |  |

| Variable Character<br>String |     |                                       |    |                                    |     |  |

Table 2 Division of Instructions

|                                           | Instructions<br>Implemented in<br>CPU Chip | Instructions<br>Implemented in<br>Floating Point Chip | Instructions<br>Implemented in<br>Macrocode |

|-------------------------------------------|--------------------------------------------|-------------------------------------------------------|---------------------------------------------|

| Percent by Instruction Count              | 57.6%                                      | 23.0%                                                 | 19.4%                                       |

| Percent by Microword<br>Count             | 20.0%                                      | 20.0%                                                 | 60.0%                                       |

| Percent by Typical<br>Execution Frequency | 98.1%                                      | 1.7%                                                  | 0.2%                                        |

be the first single-chip CPU with full demandpaged virtual memory support right on the chip. At first the design team proposed to use a simplified version of VAX memory management. During the course of the design, however, the software engineers reported that not providing full memory management was quite expensive in terms of the use of physical memory. Therefore, the design team implemented full VAX double-mapped compatibility in the chip. As the design progressed, it became evident that the incremental cost of providing this capability was much lower than originally anticipated.

All existing VAX processors implement memory management with a large address translation cache (at least 128 entries), with system and process addresses in separate halves. A translation cache must have a high hit rate to be effective. Since most caches are direct mapped, many entries are required to achieve a high cache rate. The Implementing a comparable number of translation cache entries in the 78032 was out of the question, due to die size constraints. However, the VLSI technology in the 78032 is very amenable to using a fully associative translation cache with least-recently-used (LRU) replacement.

Such a cache needs many fewer entries to achieve the same hit rate as the direct-mapped version. In addition, the tight coupling to local memory, as explained in the next paragraph, made it possible to reduce drastically the amount of time required to process a translation cache miss. Thus the translation cache in the chip has only eight entries, but the cache is fully associative, uses true LRU replacement, and is supported by highly optimized microcode for fast processing of misses. More-

over, simulation studies showed that the best use of the eight entries was with a homogeneous structure. Therefore, the system and process addresses are cached together.

The team also decided to forgo the use of an external memory cache, which required a complex external interface. Use of an internal memory cache had already been ruled out due to die size constraints. Accordingly, the speed of memory access is 400 ns, or two microcycles, which is the speed of local memory. Thus the chip encounters no wait states, and its average time to access memory is approximately the same as the 11/780's. In a typical program, there is little difference between the integer instruction performance of the two CPUs.

Additional simplifications included the elimination of warm (microcoded) floating point in favor of a floating point accelerator, elimination of writable control store capability, and elimination of on-chip console support.

#### Design Narrative

The starting point for the chip design was the instruction execution chip of a multichip VLSI VAX processor already in design. This chip would provide a general floorplan and a base microarchitecture, and might even provide complete design sections that could be used for the MicroVAX 78032. As the project progressed, the designs of the VLSI VAX processor and the MicroVAX 78032 tended to diverge under the pressure of differing constraints: chip set and system functionality for the former; die size, power, and time to market for the latter. Ultimately, only part of the main datapath was shared between the two; the rest of the MicroVAX 78032 design and its microcode were unique.

The MicroVAX 78032 project took 20 months from start to first-pass mask generation: 6 months for specification and general design, and 14 months for physical implementation. Eighteen people worked on the design team.

# Project Design Tools

The design team was aided by a hierarchical CAD tool suite that ran on a VAX system. The use of these tools was one of the primary reasons that the project was completed on schedule. The principal components of this tool suite are as follows:

- 1. A proprietary chip-database manager and tool interface called the CHAS system

- 2. A schematic capture program, QUICK-DRAW, that uses simple terminals

- A proprietary hierarchical simulator called the DECSIM system, used for behavioral simulation

- 4. A switch-level MOS logic simulator, RSIM, used for unit-delay logic simulation

- A modified version of the standard SPICE circuit simulator that incorporates new analytical, rather than empirical, MOS transistor models

- Design-rule checking programs, DRC and DRACULA II

- An interconnect verification program called the IV system, which performs both layout extraction and wiring verification<sup>9</sup>

- 8. A cross-reference program, XREF, that analyzes coupling, bootstrap ratios, dynamic node stability, and other circuit problems

The chip layout was done on Calma GDS II systems. Three dedicated VAX-11/780 systems and five Calma stations were used throughout the project. The back-end verification of circuits and the layout required as many as eight VAX systems.

## Final Chip Design

The final product of this design process is a microprocessor that contains 125,000 transistor sites in a 3-micron, double-metal NMOS chip that measures 8.7 by 8.6 mm. It requires

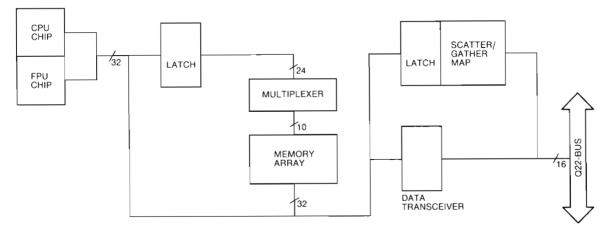

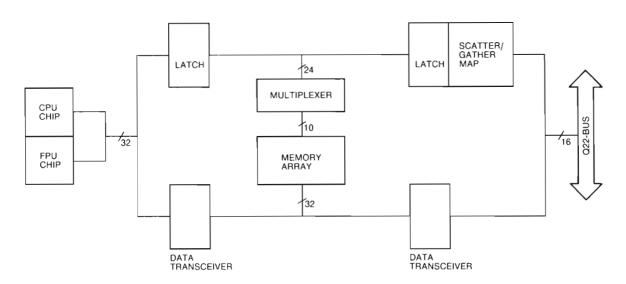

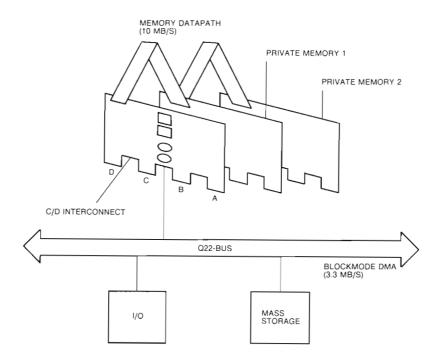

only 5 Vdc and a maximum of 3 watts of power; it is packaged in a 68-pin, surface-mounted leaded chip carrier. The chip operates at 20 MHz and has full 32-bit internal and external datapaths. The 78032 is mounted on a single-board, quad-sized (8.5 by 10.5 in.) CPU module having a Q22 I/O bus and 1 megabyte (MB) of local memory. An optional FPA, the MicroVAX 78132 chip, can also be mounted on the CPU board.

The measured speeds of integer and floating point operations of the 78032 represent a breakthrough in 32-bit microprocessors. System evaluations of MicroVAX 78032 modules indicate that their performance in processing integers is approximately equal to that of the VAX-11/780 system. With the floating point chip, the performance is between those of the VAX-11/750 and VAX-11/780 systems with FPAs.

The remainder of this paper explains the functional organization of the chip and its physical implementation in silicon.

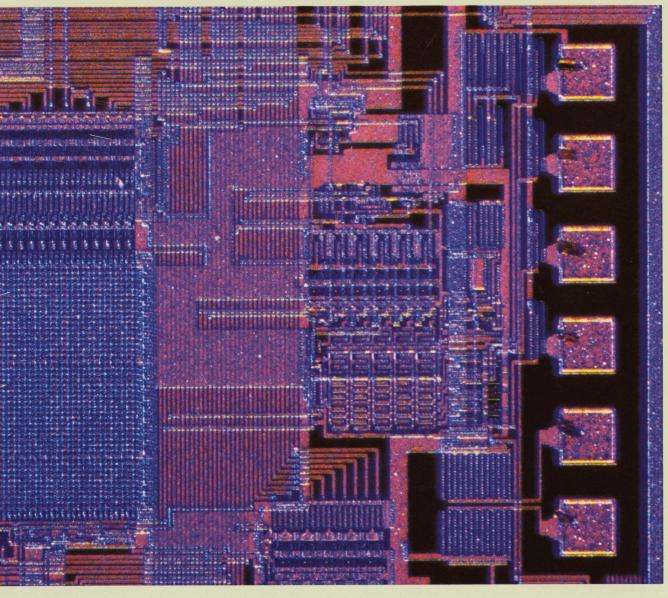

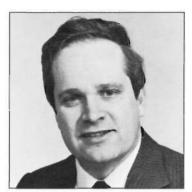

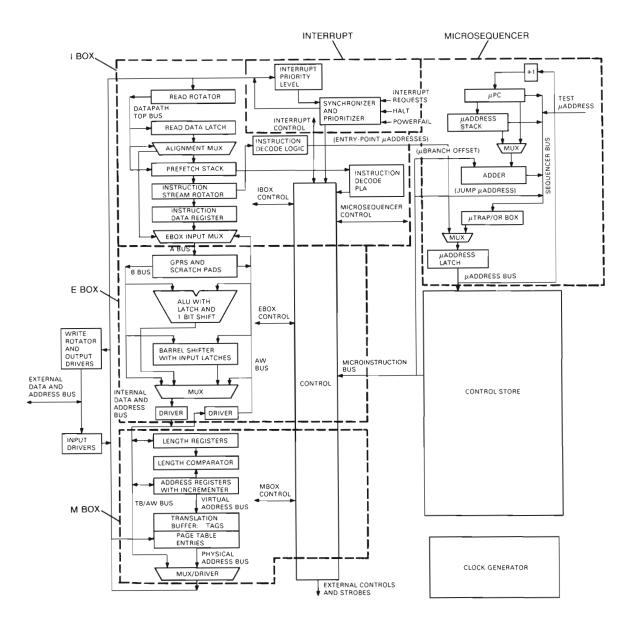

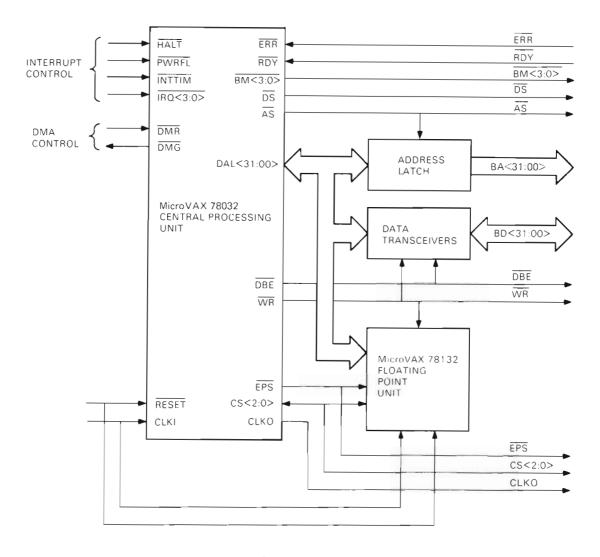

# **Functional Organization**

The diagram in Figure 1 and the photomicrograph in Figure 2 outline the various subsections, or functional boxes, of the MicroVAX 78032 chip. They are organized into three sections. At the left of Figure 2 are the datapaths for decoding and executing instructions and for memory management. At the center is the control logic for internal operations and the protocol signal logic for external operations. At the right is the sequencing logic for both internal and external operations.

The left section in the photomicrograph (Figure 2), comprising the datapaths, consists of the I Box, the E Box, and the M Box.

The I Box prefetches and decodes instructions. Its main function is to parse the current macroinstruction in the instruction stream and work in conjunction with the microsequencer to generate the microaddress for the next microinstruction. This microaddress is a function of the current macroinstruction. A prefetcher, which works in parallel with other chip operations, accesses and stores instruction data in an eight-byte prefetch queue. The prefetcher acts autonomously by attempting to keep that queue full at all times, using any free I/O-bus cycles to access the instruction

Figure 1 Block Diagram of the CPU Chip

stream. Even if the queue is full, the prefetcher will start to read data if the queue will be at least half-empty after the current microcycle.

The I Box also decodes instructions and variable-length operand specifiers in parallel with other chip operations. That avoids requiring explicit decode cycles to execute successive macroinstructions. Due to the constraints on the size of the control store, most of the address-specific microcode had to be shared among all instructions. The

instruction-decode PLA (IPLA) generates 19 bits of opcode-specific data for controlling other chip operations related to a given instruction. That allows many microcode sequences to be table driven and shared.

The E Box is the instruction execution unit and contains the main datapath of the chip. This box holds 16 VAX-specified general purpose registers (GPRs), 20 microcode registers, a 32-bit arithmetic logic unit (ALU), and a 32-bit barrel shifter. The E Box also maintains condition codes for the process

Figure 2 Photomicrograph of the CPU Chip

status longword (PSL) and determines VAX branch conditions at the macrocode level. In a 200-ns cycle, the E Box can read two registers, perform an ALU operation or shift, and write the result into a register. Since reading and writing to registers are performed sequentially, the ALU result bus is multiplexed with an input bus, thus saving vertical interconnect. The ALU employs a 4-bit lookahead carry scheme, with ripple carries across the nibbles. The carry chain uses dualrail logic for maximum speed. The barrel shifter is a pass-transistor network, which is very compact and fast enough for this task.

■ The M Box serves as the memory management unit and translates virtual addresses to physical addresses. The address translation cache, which is fully associative, stores the most recently referenced address translations. The M Box maintains three virtual address registers, one for instruction data and two for program data. This unit also detects cross-page accesses and includes a separate comparator for length checking. A dedicated adder generates the next virtual address for sequential data and instruction addresses. The time to perform an address translation is less than 25 ns when the virtual address is in

the translation cache. This short translation time allows memory management to be transparent to the external chip timing.

The center section of the photomicrograph is composed mostly of random control logic. That logic translates the highly vertical (39-bit) microcode into the many discrete control signals required to operate the datapath.

The right section of the photomicrograph, comprising the sequencing and clocking logic, consists of the interrupt logic, the control store, the DAL interface, and the clock generator.

The interrupt logic accepts, synchronizes, and prioritizes external interrupt requests, compares them with the current interrupt priority level (IPL), and determines if the request will be serviced. The interrupt requests are checked at the beginning of each microcycle and the interrupt update is forwarded to the I Box. That all happens through the central control logic before the next microcycle begins.

External interrupt processing has been implemented on-chip in the 78032 to avoid the complexity that results from having the interrupt priorities arbitrated outside the chip. Since these priorities are an integral part of the processor state, an off-chip design would involve broadcasting the interrupt priority level each time it changed. Moreover, off-chip interrupt processing would also require additional hardware on the CPU board.

- The microsequencer accepts inputs from various points on the chip and generates the next microaddress to access the control store. The microsequencer logic performs such operations as microsubroutine calls and returns, microcode traps, n-way (or case) branches, and signed offset conditional branches. Implemented in the microsequencer is an eight-level microprogram stack.

- The control store is a 39-bit ROM with 1600 entries. It receives microaddresses and status signals and generates the next set of microinstructions. The control store transfers those microinstructions to the control section in the center area. That section, in turn, generated.

ates control signals for the three principal functions in the main datapath: the I Box, the E Box, and the M Box. The access time of the control store is less than 100 ns.

- The DAL interface handles all control signals and transfers data and addresses between the chip and local memory, peripherals, and other devices outside the chip. The DAL interface transparently processes variable-length operands and aligns data references that cross natural 32-bit memory boundaries. It also causes the microprocessor to stall during I/O references, so that additional microcode is not needed to test for I/O completion. The DAL interface controls transactions involving the CPU chip, the FPU chip, and external devices. It also arbitrates direct memory access (DMA) requests.

- The clock generator receives an external 40-MHz clock reference and produces the eight 25-ns clock phases that time functions on the chip. The control logic of the chip makes extensive use of bootstrapped drivers. For that reason, certain clock phases have to drive very high capacitances, as much as 250 picofarads. To assist in that task, a special driver circuit with current-limiting resistors is used to provide fast edges without using excessive power or silicon area. These resistors control the overlap current drawn during bootstrapping and provide a voltage drop during the overlap.

## External Interface

A principal goal in designing the chip's external interface (Figure 3) was to demand as few support functions as possible from the CPU board. The 78032 chip provides seven hardware interrupt inputs. Four of these inputs (IRQ<3:0> L) correspond to standard VAX I/O interrupts and result in vectored interrupt transactions. Three others (INTTIM L, PWRFL L, HALT L) have preassigned interpretations and the corresponding vectors are generated inside the chip. The 78032 takes in a double-frequency clock input from a standard oscillator. The chip produces a normal-frequency clock output, which can be used to drive or synchronize external logic. The functions between the chip and the Q-bus can be implemented in offthe-shelf discrete logic.

Figure 3 External Interface

Except for the 32-bit DAL bus, the external interface closely resembles those for existing 16-bit microprocessors. Specifically, its timing and signal complement are quite similar to those in current machines. The addresses and data on the DAL are time division multiplexed, with separate timing strobes (AS and DS, respectively, in Figure 3). The data direction and the data buffer signals (WR and DBE in Figure 3) are used to control external transceivers directly. The cycle status signals differentiate among the various types of bus transactions. Four-byte mask signals, one for each group of eight bits on the DAL bus, allow straightforward manipulation of bytes within longwords (four bytes).

The RDY signal allows slower peripheral devices on the I/O bus to stretch the memory access time beyond 400 ns until they are ready to respond.

#### Parallel Operation

Besides giving the 78032 optimized microcode and a fast microcycle time, the design team enhanced the chip's performance by allowing parallel operations between and within functional subsections. This parallel flow is actually a form of pipelining in which the operations happen independently and concurrently. For example, while the E Box is executing a datapath operation, the control store can access the next microinstruction. At the same time, the

microsequencer can be calculating the address of the microinstruction after that one, and the M Box can be translating a virtual address. Meanwhile, the I Box can be decoding an instruction or operand specifier and prefetching more instruction data. And the DAL interface can be initiating or completing an external bus operation.

For example, assume that the chip is to execute the following two three-microcycle macroinstructions in sequence:

ADDL3 R0, R1, R2 SUBL3 R4, R5, R6

Within the third 200-ns microcycle, some operations associated with these two macroinstructions are performed in parallel by several subsections. The E Box will write the result of ADDL3 into R2 in the register file, set the PSL condition codes, and check for arithmetic exceptions, such as an overflow trap. Meanwhile, the I Box will decode the next macroinstruction, SUBL3, and its first specifier, R4. Concurrently, the prefetcher in the I Box will determine if the decode of the instruction and specifier will clear enough space in the prefetch stack to warrant another longword transfer. If so, the I Box will then initiate the transfer and fetch another macroinstruction. which also involves the DAL interface.

Within each subsection, there are also a number of parallel operations that reduce the overall execution speed significantly. In addition to simultaneous prefetch and decode actions in the I Box (as described above), the microcode access in the control store is pipelined: The next microaddress is accessed while the current microinstruction at the current microaddress is being executed. In the M Box, length checks against referenced addresses take place simultaneously with the translation cache lookups. If a lookup misses, therefore, the length check will have already determined whether or not the referenced page is within range. In the E Box, a separate program counter (PC) adder maintains the PC so that the ALU can be dedicated to its primary task.

Some typical execution times for instructions under normal operating conditions (aligned operands, no memory management exceptions) are as follows:

| Instruction                         | Operands | Typical<br>Execution Time<br>(Nanoseconds) |

|-------------------------------------|----------|--------------------------------------------|

| MOVL                                | Reg, Reg | 400                                        |

| ADDL2                               | Reg, Reg | 400                                        |

| MOVL                                | Mem, Reg | 800                                        |

| ADDL2                               | Mem, Reg | 800                                        |

| MOVL                                | Reg, Mem | 600                                        |

| ADDL2                               | Reg, Mem | 1200                                       |

| Conditional<br>Branch,<br>not taken |          | 200                                        |

| Conditional<br>Branch,<br>taken     |          | 800                                        |

# Physical Implementation

The MicroVAX 78032 chip is made using a 3-micron, double-metal NMOS process that allows power savings and superior circuit flexibility. Until the MicroVAX 78032 chip design, single metal was a standard for NMOS technology. The use of a second layer on the 78032 chip was a significant departure for NMOS design. There are two main advantages of a double-metal implementation. First, it is easier to place logic circuits in the interconnect layer, where there are more circuits per unit area of silicon. Second, the metal interconnect has lower resistance than polysilicon, thus avoiding wire delays that are difficult to eliminate in design.

The double-metal process provided the chip design team with two layers of aluminum interconnect and four types of devices (N, E, L, and D). The four types allow some savings in power and a substantial increase in circuit flexibility. However, the E device (light enhancement) is typically used only in source-follower circuits, and the L device (light depletion) only in latches and static memories. The second layer of aluminum interconnect manages the complexity associated with 32-bit microprocessors. That permits global communications and allows local control or routing to share the same chip area. However, second metal can only contact first metal, and then only through an offset, or staggered, contact.

Figure 4 X-shaped Cells

The control store is a 1600-entry by 39-bit ROM. Although its size was decreased mostly through repartitioning and optimized microcode, about ten percent of the reduction was gained through the cell structure chosen. X-shaped cells with a virtual-ground design were used (Figure 4). This ROM has no physical ground, whereas standard ROMs with H-shaped cells have one ground line for every two data lines. The X-shaped cell, which is 95 microns square, is also more dense than the standard cell. Moreover, in the X-shaped cells, second metal is strapped across the top of the array to minimize the row propagation time. The cell access time is 100 ns.

The ROM bit lines are precharged to  $V_{CC}$  using depletion pullups. Sensing is done with a cross-coupled stage using local depletion divider voltage references set at  $0.6 \times V_{DD}$ . Column access occurs in 25 ns.

The control circuits (at the center in Figure 1) are implemented in dynamic logic so that the total power dissipation is kept below three watts. That also allows a low-cost packaging design. The eight clock phases provide refresh timing references to the dynamic logic.

Due to tight silicon constraints, the test features built into the design had to be limited in scope. The principal ones used are as follows:

- Serial shift registers with feedback for observing the control store, IPLA, and microsequencer outputs

- Special test mode for overriding normal sequencing with external microaddresses

- Dedicated microcode for optimizing state observations in the special test mode

# Summary

The MicroVAX 78032 represents a major breakthrough both in semiconductor technology and in the VAX family. From a technology perspective, it is the first implementation of a successful 32-bit superminicomputer on a single chip. It is the first chip to provide integral demandpaged virtual memory management. And it is the first chip to provide system performance comparable to the 11/780. From a VAX perspective, the 78032 is the key to the downward extension of the industry-standard VAX family into the realm of small systems and workstations.

# Acknowledgements

The authors acknowledge the technical contributions of John Beck, Sandy Carroll, Gerry Cheney, Mary Jo Doherty, John Glynn, Jim Gorr, Bob Grondalski, Dave Grondalski, Pat Hart, Ernie Hohengasser, Taan Lee, Steve Morris, Tony Pasquito, Steve Thierauf, Tim Thrush, Janet Vitello, and Barry Worster.

### References

- VAX Architecture Handbook (Maynard: Digital Equipment Corporation, Order No. EB-19580, 1981).

- 2. W.N. Johnson, "A VLSI Superminicomputer CPU," *IEEE International Solid-State Circuits Conference Digest of Technical Papers* (1984): 174-175.

- 3. J. Slager et al., "A 16-bit Microprocessor with On-chip Memory Protection," *International Solid-State Circuits Conference Digest of Technical Papers* (1983): 24-25.

- 4. H.M. Levy and R.H. Eckhouse, Computer Programming and Architecture: The VAX-11 (Bedford: Digital Press, 1980).

- 5. D.W. Clark and J.S. Emer, "Measurement and Analysis of Instruction Use in the VAX-11/780," *IEEE Proceedings of the 9th Annual Symposium on Computer Architecture* (1982): 9-17.

- 6. J.S. Emer and D.W. Clark, "A Characterization of Processor Performance in the VAX-11/780," *IEEE Proceedings of the 11th Annual Symposium on Computer Architecture* (1984): 301-310.

- 7. W.D. Strecker, "Transient Behavior of Cache Memories," ACM Transactions on Computer Systems, vol. 1, no. 4 (November 1983): 281-293.

- 8. D.W. Clark, "Cache Performance on the VAX-11/780," ACM Transactions on Computer Systems, vol. 1, no. 1 (February 1983): 24-37.

- 9. G.M. Tarolli and W.J. Herman, "Hierarchical Circuit Extraction with Detailed Parasitic Capacitances," ACM IEEE 20th Design Automation Conference Proceedings (1983): 337-345.

# The MicroVAX 78132 Floating Point Chip

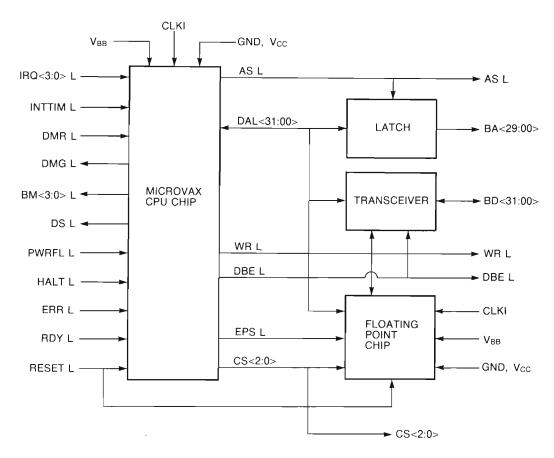

A separate chip, the 78132, in the MicroVAX II system performs fast floating point calculations. Three datapaths, each controlled by microcode, work in parallel to yield a 100-nanosecond microcycle. The wide datapaths accommodate a large variety of instructions, using microwords of only 35 bits for control. The 78132 is a 3-micron NMOS chip connecting to the CPU chip of the MicroVAX II system via a general-purpose protocol and a limited set of lines. Crosstalk and resistivity posed particular design problems, as did the routing of signals and power. The 78132's electrical integrity was carefully checked to ensure high reliability.

Scientific and engineering applications require strong floating point support from their computers. All VAX implementations offer both microcoded (warm) and hardware (hot) capabilities to execute the 95 floating point instructions in the full VAX instruction set. The MicroVAX II processor also supports floating point instructions, but in a slightly different fashion. Since the control store in the microprocessor, the CPU chip, has a limited size, these instructions are not executed in microcode; instead they are emulated in macrocode. 1,2 Emulation is relatively slow and does not provide the fast speeds required for intensive mathematical applications. Therefore, a separate floating point accelerator (FPA), the MicroVAX 78132 chip, has been developed as a companion to the CPU chip, the MicroVAX 78032 chip.

The 78132, or FPU chip, is designed to provide fast floating point calculations on a single chip. It executes 61 of the 70 floating point instructions in the MicroVAX instruction set. Nine of the 70 instructions simply move data, and the CPU chip does not need the FPU chip to handle them. The FPU chip also accelerates calculations for 9 integer instructions, which are associated with integer multiplies and divides. The FPU chip executes instructions about 100 times faster than macrocoded emulation.

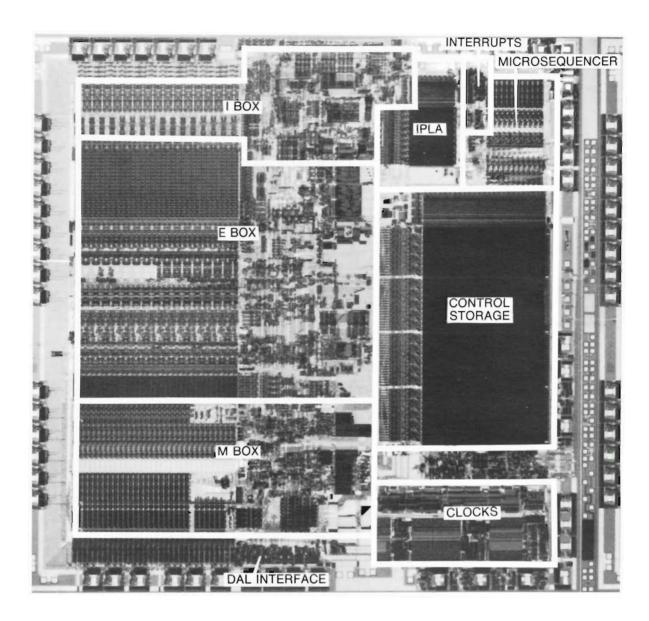

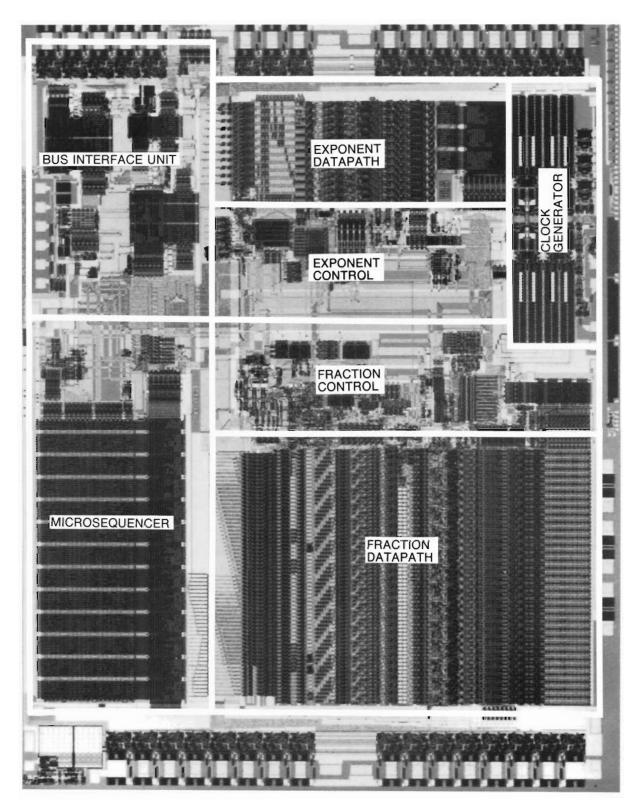

The FPU chip (Figure 1) contains 32,141 transistors in a 3-micron, double-metal NMOS chip, which requires just under 2 watts of power at 5 Vdc. It measures 8.4 by 6.6 mm and is packaged in a 68-pin leaded chip carrier. The chip has a 100-nanosecond (ns) microcycle, divided into four 25-ns clock phases generated from a 40-MHz input clock. The CPU chip, which also operates on a 40-MHz input clock, has a microcycle of 200 ns. The faster microcycle and wide datapaths enable the FPU chip to perform floating point operations much faster than the CPU chip with its general datapath.

This paper discusses the implementation of floating point in the MicroVAX II's FPU chip and the unique constraints of a single-chip floating point accelerator. These constraints are not limited only to architecture but include interface design, wiring, and signal integrity, all areas where design trade-offs are important.

At the highest level, the FPU chip implements the F, D, and G floating point instructions in the VAX instruction set. The chip is constrained by the requirements of the VAX architecture—data formats, accuracy requirements, and instruction vagaries—and by the characteristics of the technology—limited number of pins, limited die size, and limited inter-

Figure 1 Photomicrograph of the FPU chip

connect. These constraints dictated many of the design considerations in the FPU chip.

# FPU Chip Architecture

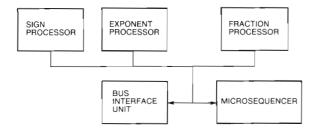

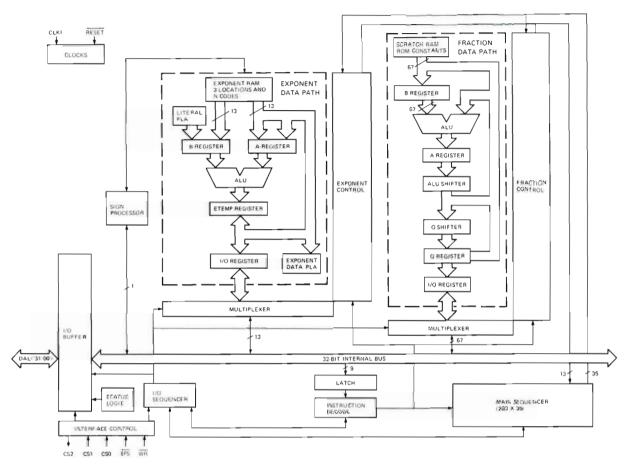

The main elements of the FPU chip, shown in the block diagram in Figure 2, are similar to those in most floating point devices.<sup>3</sup> Three separate processors—a 67-bit fraction processor, a 13-bit exponent processor, and a single-bit sign processor—operate in parallel. The bus interface unit handles data transfers over the external bus to the CPU chip and data movement into and out of the three datapaths. The microsequencer controls the parallel operations of the processors.

Each element in the FPU chip operates in parallel to speed up instruction processing. The microsequencer steps through the microcode for an instruction and determines which operation is to be performed by each processor for the current cycle. The microsequencer also takes inputs from each of the processors to determine which microword is to be executed next. The datapath of the fraction processor performs all the arithmetic computations on the mantissa of a floating point number. This datapath is designed to be flexible enough to handle the many different operations required in a general-purpose FPA. The datapath is also segmented to handle the F, D, and G data types, and is optimized to provide the maximum possible performance from the N-channel MOS technology.

The datapath of the exponent processor handles only the exponent portion of a floating point number. The exponent datapath is also used as a counter during certain operations such as multiply and divide. This datapath does all the exception and bounds checking for operations like addition and subtraction. The sign processor is incorporated into the expo-

Figure 2 Block Diagram of the FPU chip

nent datapath and handles all operations pertaining to the sign bit. During an addition or subtraction, the sign bit determines which case is performed by checking the signs of the two operands and the opcode of the instruction.

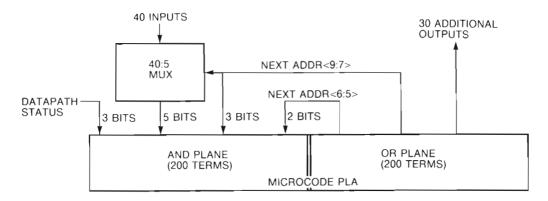

The bus interface unit (BIU) is responsible for handling all the FPU portions of the bus traffic between the FPU and CPU chips. The BIU decodes the opcode sent to the FPU chip and tells the microsequencer which instruction to execute. That allows the FPU and CPU chips to coordinate their actions without a lot of protocol or pins. Since many different data types are processed, the BIU is responsible for unpacking the operands and steering them to the appropriate datapath. Once the instruction is completed, the BIU takes the unpacked result from each datapath and formats the result into the specified data type. Figure 3 contains a more detailed block diagram for the entire floating point unit.

# Algorithms

To keep the FPU chip at a size that could be produced, we decided not to use special-purpose hardware to implement instructions like addition or multiplication. Instead, the datapaths are designed to be general-purpose ones to accommodate the needs of a wide variety of instructions.

#### Addition and Subtraction

The datapaths are under microcode control and work in parallel. Within each, the steps required for either addition or subtraction are done serially. First, the exponents of the two operands are compared to see if they are of equal magnitude. If not, the larger exponent is stored in a register, and the exponent difference is used to control the alignment. The shifter on the output of the fraction arithmetic logic unit (ALU shifter) allows the fraction with the smaller exponent to be aligned five bits at a time. During each alignment step, the exponent difference is reduced by up to a magnitude of five until the exponents are equal. Once equal, the fractions are added. (In subtraction, the fraction to be aligned is complemented before alignment.)

The resulting fraction is then normalized. The normalize shift is accomplished by a single left shift in the fraction ALU and two left shifts in the ALU shifter. If the addition of the

Figure 3 Block Diagram of the FPU Processor

fractions results in an overflow into the top guard bit, a single right shift in the ALU shifter is required to normalize the result. During normalization, a 3-bit code is sent to the exponent datapath, which determines the amount the exponent must be adjusted.

After normalization, the fraction is rounded using a rounding constant appropriate for the data type of the floating point operation being performed. If the round results in an overflow in the fraction datapath, the exponent is incremented by one and the fraction is normalized. The exponent datapath then checks the resulting exponent for any error conditions. If no errors are found, the final fraction and exponent values are loaded into the output register and the sequencer signals the BIU that the operation is complete.

#### Multiply

The multiply operation in the FPU chip is based on a 3-bit retirement algorithm. The 3-bit retirement, or octal multiply, must generate the required multiple, 0-7, of the multiplicand to be added into the partial product for each step. The multiples must be generated by simply shifting the multiplicand and adding or subtracting them from the partial product. The multiples 0, 2, 4, and 8 are easy to generate in this way. The multiple 6 can be formed by taking three-quarters of the multiplicand and storing that in a register at the beginning of the multiply  $(34 \times 8 = 6)$ . As shown in Table 1, all the even multiples can be generated. To generate all the odd multiples, a - 1 multiple is added to achieve the final exact multiple for each retired group of three bits.

Table 1 Multiply Operation - Booth Encodings

| Multiplier<br>Group | Required<br>Multiple | Data<br>Used | Multiple<br>Shift | Multiple<br>Added | Multiple<br>Owed |

|---------------------|----------------------|--------------|-------------------|-------------------|------------------|

| 000                 | 0                    | 0            | 0                 | 0                 | 0                |

| 001                 | 1                    | mult         | 1                 | 2                 | -1               |

| 010                 | 2                    | mult         | 1                 | 2                 | 0                |

| 011                 | 3                    | mult         | 2                 | 4                 | -1               |

| 100                 | 4                    | mult         | 2                 | 4                 | 0                |

| 101                 | 5                    | 3/4 mult     | 3                 | 6                 | -1               |

| 110                 | 6                    | 3/4 mult     | 3                 | 6                 | 0                |

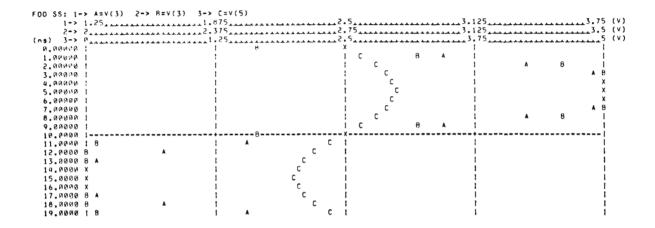

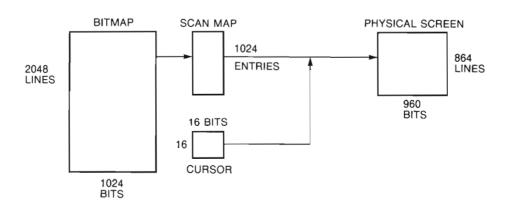

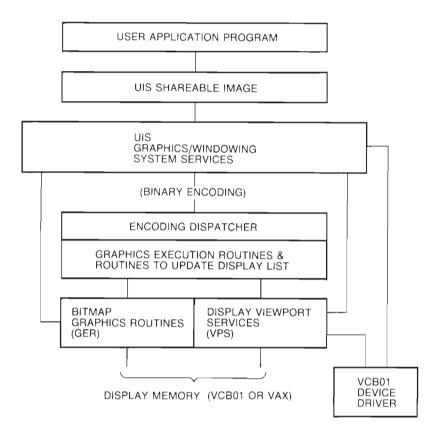

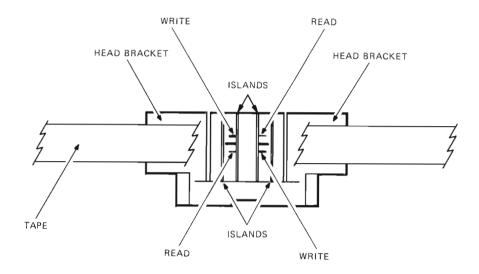

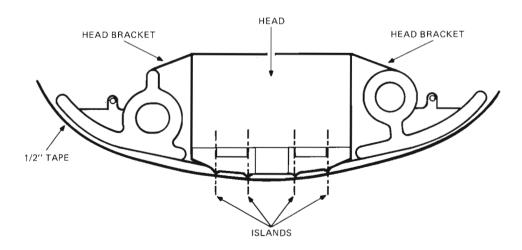

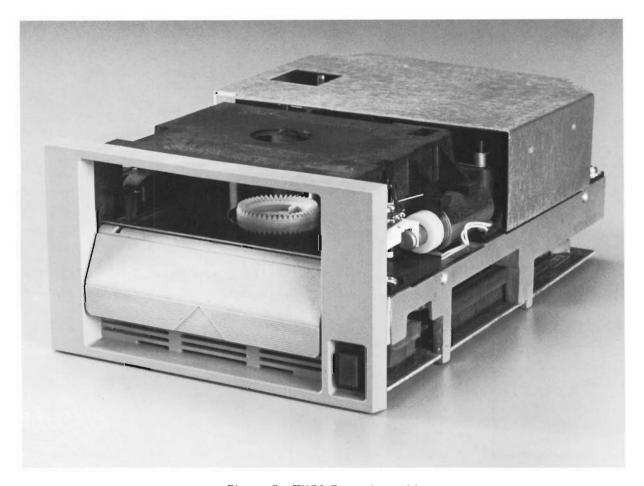

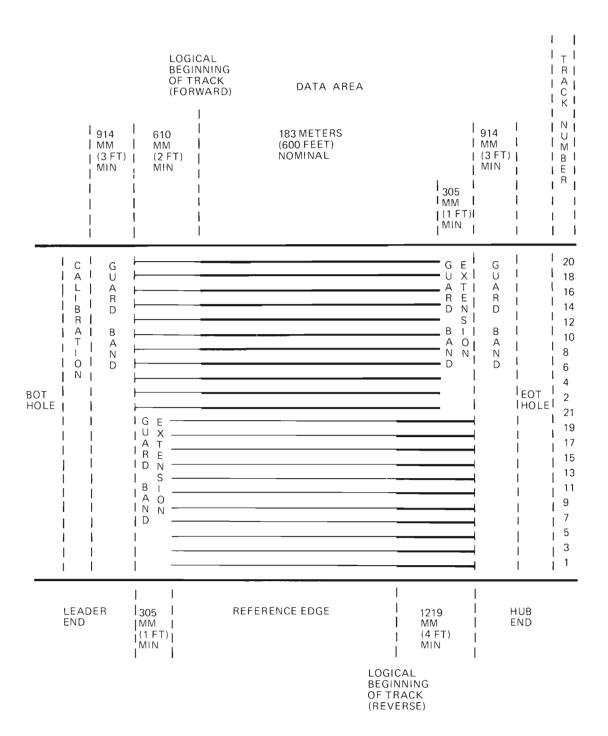

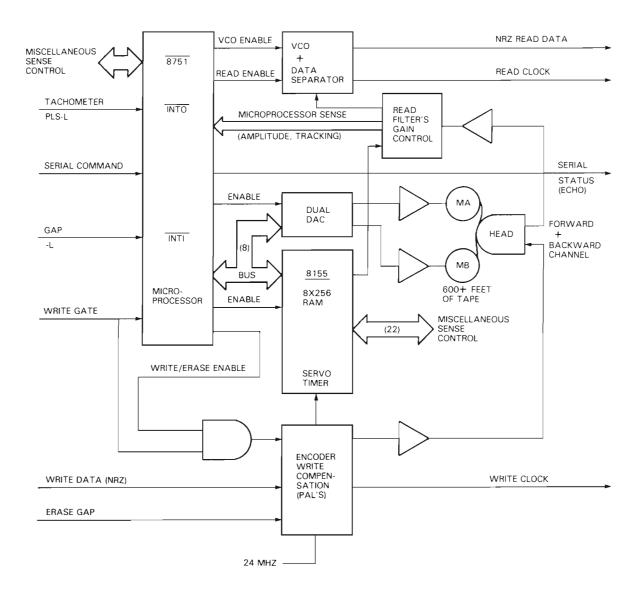

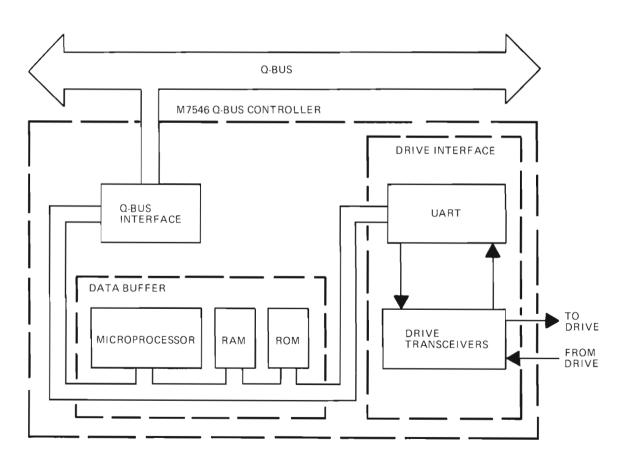

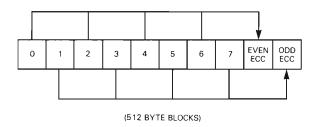

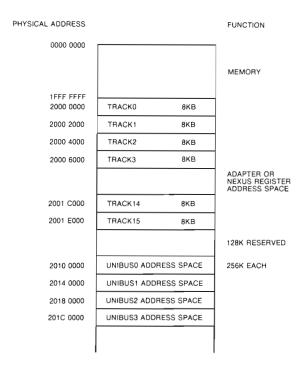

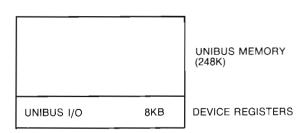

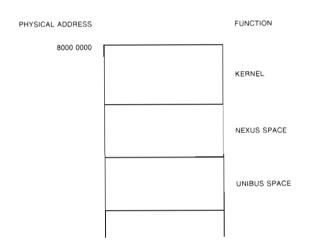

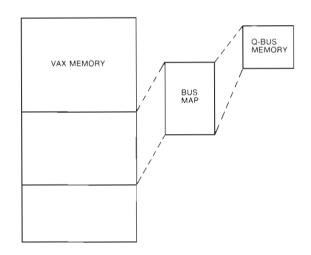

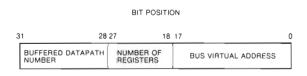

| 111                 | 7                    | mult         | 3                 | 8                 | -1               |